# **Virtuoso Layout Editor**

This tutorial will cover the basic steps involved in using the Cadence layout editor called Virtuoso, extracting layout, and running simulation on the layout. The inverter layout is used as an example in the tutorial.

Before we start, you should have necessary files and setup done to be able to run Cadence software. If you have not done this, see tutorial on "How to setup Cadence tools?" (Available on class website)

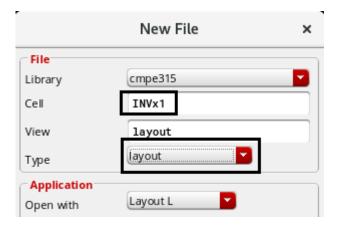

## **Create New Layout View**

To create a layout view, go to **File -> New -> Cell View**, select the **Layout** tool in the tool selection menu and type in Cell Name as shown in Figure 1. Click OK, a windows will pop up; with a layout view and LSW on the left. The layout window is the main window where you do your design layout. The LSW or the layer selection window gives you a list of all available layers in the current technology. They will include layers like poly, nactive, pactive, nselect, pselect, metal1, cc, via etc. depending on the technology you are fabricating in.

Figure 1: New Cell View

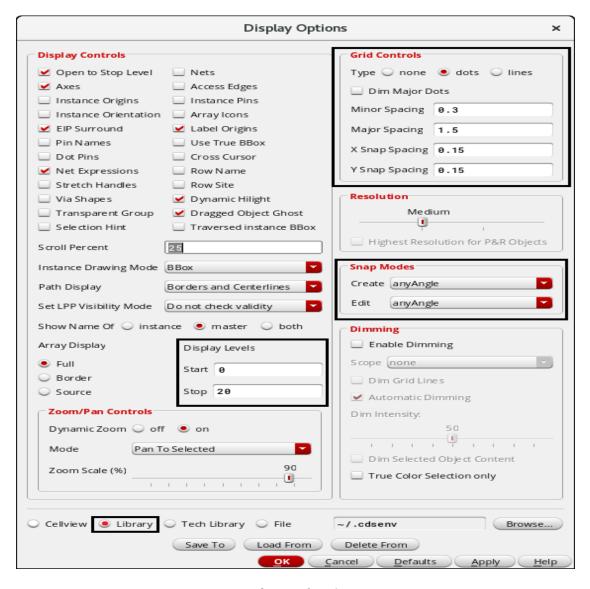

# **Setup Display Options**

To start the layout the first thing that you need to do is fix your grid sizing. Go to **Options -> Display**, the options window shown in Figure 2 will pop up. Set the grid control parameters in the right hand upper corner to the following values.

```

Minor Spacing = \lambda

Major Spacing = 5\lambda

X Snap Spacing = \lambda/2

Y Snap Spacing = \lambda/2

```

Remember  $\lambda$  is half the feature size so if you are using a 0.6  $\mu$ m. process then the  $\lambda$  value is 0.3. Also make sure that the **Snap Modes Create and Edit** settings in the right bottom corner are set to **anyAngle**. Set the **Display Levels** to **Start** = **0** and **Stop** = **20**. Select Library on the bottom and click **Save To**. Once you save the options to the library, you don't have to set up the display options again when working in the same library. Click OK and then go the **Window** -> **redraw** to update new setting on the screen. If you are working in **NCSU\_TechLib\_ami06** attached library, you can simply follow the setup exactly as shown in Figure 2. *Turn on the Pin Names option under Display Controls*

Figure 2: Display Options

# Getting to know Virtuoso Menu

Tools Design Window Create Edit Verify Connectivity Options Routing NCSU

The following menu items are frequently used during creating circuit layout.

#### File Menu:

- Save: save you layouts.

- *Printt*: Used to generate a postscript file for your layout for printing. Select submit and then plot options. Specify a file name and click ok. Then click ok on the main submit plot form and it will generate a ps file for you layout.

#### **Create Menu:**

- Rectangle: creates a rectangle of the layer selected in the LSW.

- *Path*: Creates a path of the layer selected in the LSW. Double click to end the path.

- *Instance*: used to import another existing cell view into this cell view.

- *Pin*: Create pins as explained in later section.

#### **Edit Menu**:

- *Undo*: undo the previous commands.

- Redo: redo undone commands.

- Move: click on any object and move it around in the layout.

- Copy: Create a copy of any object in the layout.

- Stretch: Click on the edge of a rectangle and size it.

- Delete: Delete an object in the layout.

- *Properties*: Change the properties of objects in the layout. Change the layer definitions and the changes are immediately reflected in the layout.

#### Verify Menu:

- DRC: Check the layout for design rule violations.

- *Extract*: Create a extracted view of the layout. This view is used for simulations.

- Markers: Explain: click on the marker to find out the design rule violated.

- Delete all: Remove the markers after a DRC run.

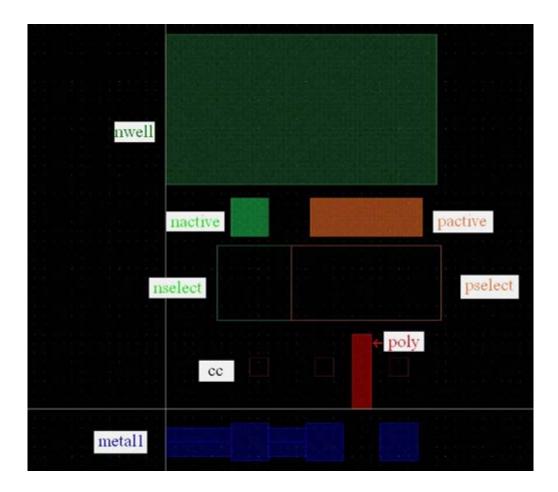

# **Drawing Transistors**

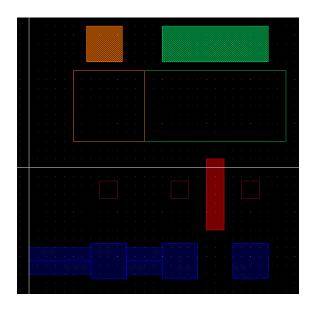

To make an inverter, first of all you need to make p and n transistors. First we will make the p transistor. Most of the technologies you will be designing in will use an n-well process. Therefore the black background in the main layout window will act as your p-substrate. Thus you can put n transistors directly in the p substrate. However your p transistor will have to be placed in n-well that you will have to draw. Figure 3 shows the different layers required to build a p transistor.

Figure 3: Layers for building PMOS

The p transistor is made using the layers as shown in the figure above. You can create each shape shown in Figure 3 by first selecting the layer you want to create on LSW window and use create rectangle command (**Create -> Shape -> Rectangle**) or create path command (**Create -> Shape -> Path**). The size of the layers depends on the DRC rules defined for the library and they can be accessed at the website: <a href="https://www.mosis.com">www.mosis.com</a>. A link is provided on the class webpage.

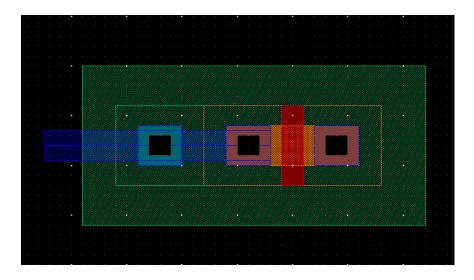

The p transistor is placed in the nwell and an n contact is placed in the nwell to connect it to Vdd. The layers needed to make the p transistor are cc, metal1, pactive, poly and pselect. The pselect region should cover the entire active area and the poly gate. The nwell should surround the entire ptransistor along with the select region. Now you need an ncontact to connect the nwell to Vdd. The ncontact is made up of cc, nactive and metal1 surrounded by a nselect rectangle. The contact is placed inside the nwell and then connected to the main Vdd supply rail in the design. The layers shown in the figure above are merged together as shown in Figure 4 to form the entire p transistor.

The order in which the layers are placed is not important the only requirement is that all the layers should be present. The layers are displayed in the layout window as defined by the tool and the overlap of two different layers will be clearly distinguishable.

Figure 4: PMOS Layout

The n transistor is laid out in a similar fashion and the layers required for the same are shown in Figure 5. However the n transistor will have an nactive layer instead of pactive layer in the ptransistor and will be surrounded by n select instead of the p select. As the technology is an nwell technology the black background is the p-substrate and therefore you need not put a pwell layer around the n transistor. However you still need to place a contact to connect the p substrate to ground. The p contact is complementary to the n contact and is made of cc, pactive and metal1 surrounded by a pselect rectangle. The combined p and n transistor are shown in Figure 6.

Figure 5: Layers for building NMOS

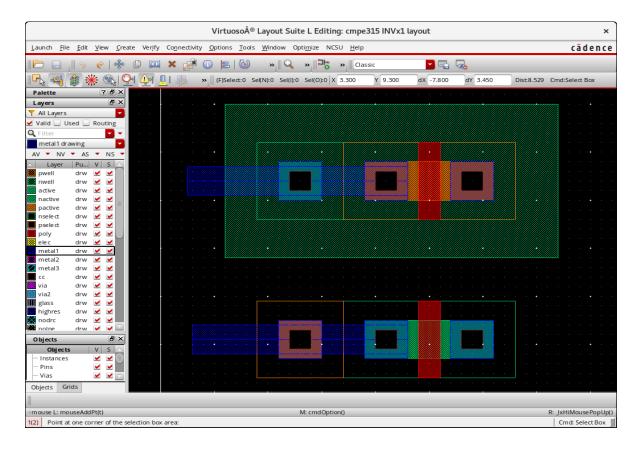

Figure 6: PMOS and NMOS layout

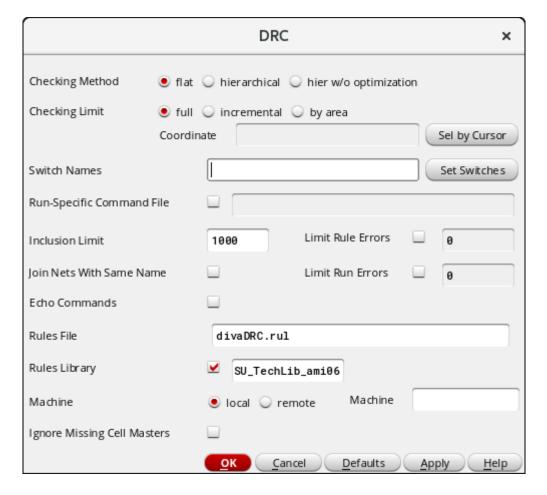

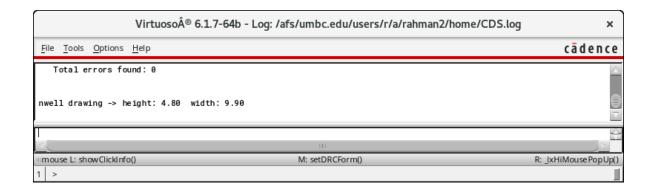

# **Design Rule Check**

There is a rule checking tool that is available with the cadence distribution which checks most of the rules. To run design rule check (DRC), go to **Verify** -> **DRC**. The DRC dialog as shown in Figure 7 should appear, click OK. Figure 8 shows DRC report displayed on CIW window, in the figure no errors are found on the design. You need to run the design rule checker at every step of you design. It is very difficult to fix up the sizes of various components after they are connected together in the layout so make sure that everything that you place in the layout is compatible with the design rules. Again the design rule for a particular technology is available on mosis website. (<a href="www.mosis.org">www.mosis.org</a>)

Most of the errors found by the design rule checker are explained in detail in the CIW window and are easy to fix. Sometimes a layout may not have DRC errors but only warnings. It is better to solve these warnings before going further. The most common warning is for pins. When you place two pins on the same path the DRC tool will generate a warning marker but will not explain it in the CIW window.

To check which marker stands for which error click on Verify - Markers - Explain and then click on any marker in the layout window. A text box will pop up specifying the design rule that is being violated. Fix the error in your layout and run DRC until your design is completely error free.

Figure 7: Design Rule Check (DRC)

Figure 8: DRC report on CIW

## **Making Connection**

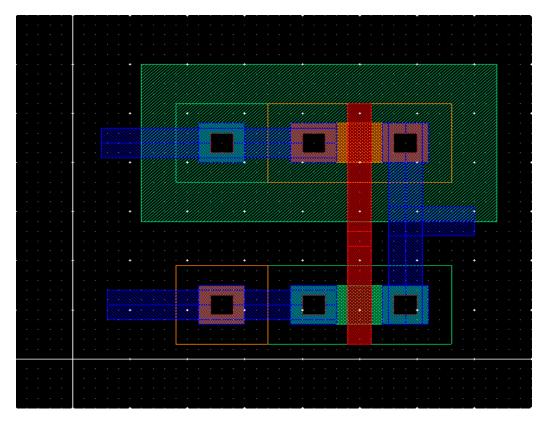

The next step to build the inverter is to connect the drains of the two transistors together to make up the output. The source of the p transistor is connected to Vdd and the source of the n transistor is connected to Gnd. The two gates are connected together to form the input of the inverter. The Path command (**Create -> Shape -> Path**) is the easiest way to connect components together in a layout. There are rules that define the minimum spacing required between two metall paths. Figure 9 shows the entire layout for the inverter.

Figure 9: Inverter Layout

- Using following shortcut keys help working with layout faster

- **r** to Create Rectangle

- **m** to Move

- s to Stretch

- **p** to Create Path

- **u** to Undo

- **c** to Copy

- To zoom in on the schematic, hold **right-botton** mouse to create zooming area and release to zoom in.

- To zoom out, press **Shift**+**z**

- To fit whole schematic on screen, press **f**

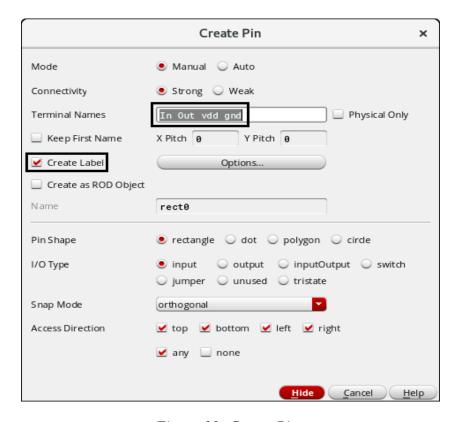

#### **Create Pins**

To complete your layout you need to place input or output pins at the various inputs and outputs of you circuit. To create pin, go to **Create -> Pin**, the dialog box as shown in Figure 10 should show up. In the **Terminal Names** box enter the name of the pins that you want to place in a space separated format (e.g. *In Out vdd! Gnd!* for the inverter). Next clicks on **Create Label** radio button to turn the option on. Next select the **I/O type** for the pin. This will have to be changed individually for each pin. Thus the pin In in the inverter will have an I/O type of input whereas the pin Out will have I/O type as output, and vdd! and gnd! will have I/O type as input/output. *You should always use vdd!* and gnd! for supply pins.

To place the pins now select the proper layer from the LSW. Thus in case of the inverter the input pin has to be placed in the poly gates connection, therefore select poly in the LSW. Now draw a small poly rectangle on the path connecting the two gates. The name associated with the pin will be displayed and click anywhere near the pin to put the name alongside the pin. Now go to the pin menu and select I/O type as output for pin out. Select metal1 from the LSW because the output is the metal1 path connecting the two drains. Create a small rectangle of metal1 on the path and place the pin name beside it. Remember that you have to place the pins in the layout in the order that you specified them in the Terminal names list in the pin dialogue box. Also remember to change the I/O type for each pin and the layer that they are to be placed in. The pins names and types should match the ones that you used in your schematic.

Figure 10: Create Pin

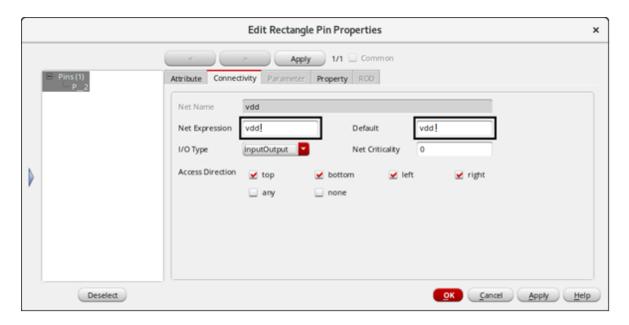

The last step is to change net name for power pins. Click on vdd! pin to select and press **q** (or go to **Edit** -> **Basic** -> **Properties**). The property dialog as shown in Figure 11 should show up, change **Net Expression Property** to **vdd!** and **Default** to **vdd!** as shown in the figure. Do the same on gnd pin, except this time change **Net Expression Property** to **gnd!** and **Default** to **gnd!**.

Figure 11: Net Expression for vdd! pin

### Virtuoso Layout Editor **Tutorial**

Saad Rahman **Chintan Patel**

- In this tutorial we use vdd! and gnd! as pin names and net names for power supply to the circuit. This is actually not required by the tool. However, if you have followed schematic design in Virtuoso Schematic Composer Tutorial, you will need to name these pins as vdd! and gnd!, so that you have same pin names for power pins in schematic and layout.

- Having different pin names in schematic and layout will cause problems when you run Layout Versus Schematic (LVS) checking tool.

- If you have created simulation view as explained in Simulation with Analog Design Environment Tutorial, naming power pins and nets as vdd! and gnd! helps avoiding recreation of simulation view. Therefore, you can use the same simulation view for both schematic and layout simulation

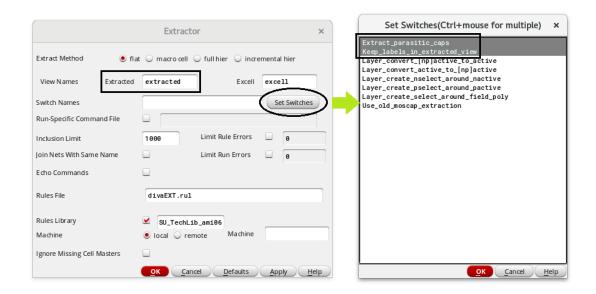

## **Layout Extraction**

The Layout extraction tool is used to generate actual circuit netlist from your layout. The extracted view can be used to run Layout Versus Schematic (LVS) and to run simulation. To run layout extraction tool, go to Verify -> Extract. The extractor dialog as shown on the left of Figure 12 should appear. Click on Set Switches and then the switches selection window should pop up as shown on the right of Figure 12. Select Extract\_parasitic\_caps and Keep\_labels\_in\_extractd\_view options as shown in the figure (hold Ctrl key and click on options to select multiple options). Click OK to close set switches dialog and click OK again on Extractor dialog to run the layout extraction.

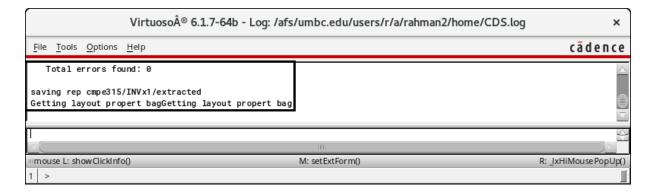

You should see extraction report on CIW window (if you have large layout, the extraction might take a few minutes before the report shows up) as shown in Figure 13. You should not have any errors/warnings, if there're any, fix it. The most common errors/warnings is having multiple pins on the same nets which means that you might have a shorting net (e.g., vdd is shorted to other nets) or have multiple pins placed on the same net (e.g., having pin named In and INPUT on the same input net).

Figure 12: Layout Extractor

Figure 13: Extraction report on CIW

#### ∠ More info:

- The extraction tool recognizes transistors by looking for the regions where poly layer overlap the active layers. (poly overlap pactive for PMOS and poly overlap nactive for NMOS). The overlap regions also define the size (width and legth) of the transistors.

- If the "Extract\_parasitic\_caps" switch turned on during extraction, the extraction tool calculates the parasitic capacitances on all layers on the layout. For example, extracting wire capacitances on the Metal wires. For some extraction rules of a particular technology, there is an option to also setting the calculation of parasitic resistances.

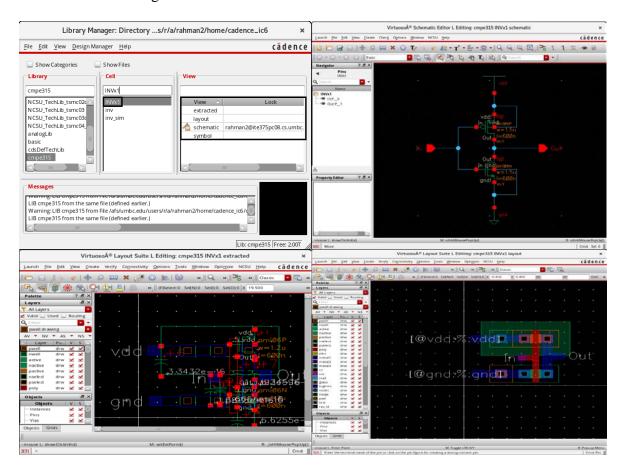

#### **Multiple Views on Cell Design**

If you have followed steps in Virtuoso Schematic Composer Tutorial and this tutorial, you should have multiple views of the inverter cell design. Each of the view represents the same circuit design but at different levels. Figure 14 shows the three (schematic, layout and extracted views) of the four cell views that you should have so far for the inverter design.

Figure 14: Multiple Cell Views of Inverter

## **Binding Extracted View to Simulation**

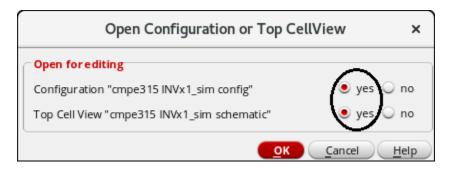

In Simulation with Analog Design Environment Tutorial, we have shown you how to create the config view for the simulation using Hierarchy Editor. Now, you can use the same cell view to switch between schematic and extracted layout (and other views that you have e.g., vhdl) in the simulation. The process used in changing cell view for the simulation is called cell binding.

Start with open the config view by double clicking on the config view from library manager. The open configuration dialog as shown in Figure 15 should appear, select yes to open both config and schematic views. On the Virtuoso Schematic window,

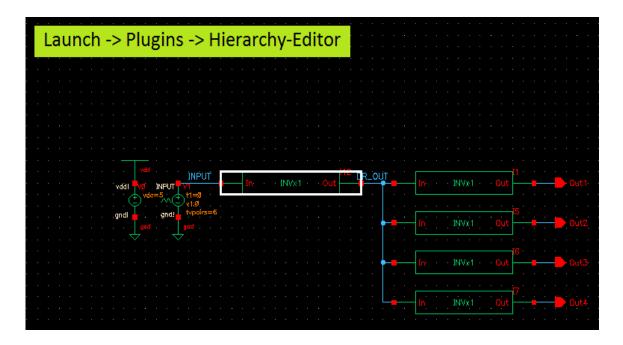

go to **Launch** -> **Plugins** -> **Hierarchy-Editor**. The Hierarchy-Editor Menu should then appear on the menu bar as shown in Figure 16.

Figure 15: Open Configuration

Figure 16: Hierarchy-Editor on Menu Bar

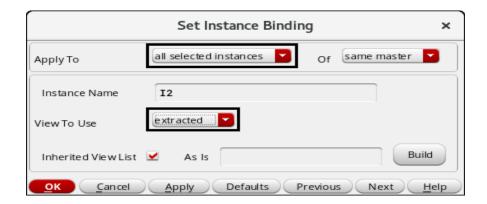

Next, click on the symbol of instance(s) you want to change the binding (you can select multiple instances by holding **Shift** key and click on multiple instances). Go to **Hierarchy-Editor -> Set Instance Binding**, the dialog as shown in Figure 17 should show up. Change **Apply To** from drop-down box to **current instance** or **all selected instances** depending on how you select the instance(s) (if you select only one instance, use current instance. If you select multiple instances, use all selected instances) and then change **View To Use** to **extracted** (or any other views that you want).

Figure 17: Set Instance Binding

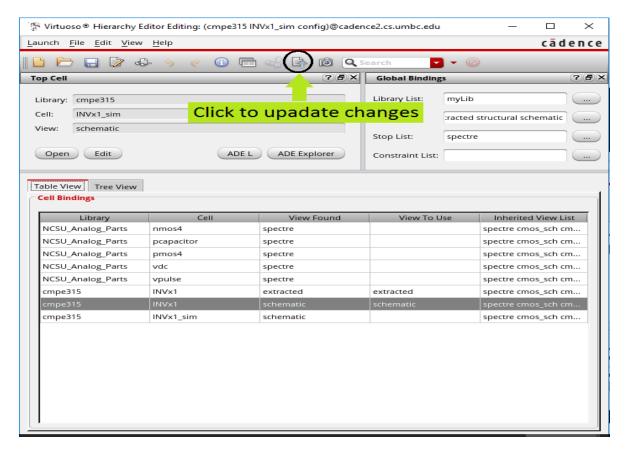

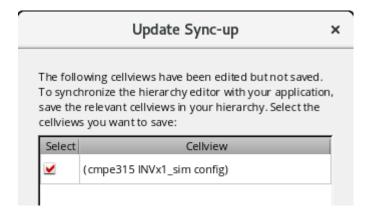

Make cell binding changes to all instances that you want and then go to Configuration window (The configuration window should have shown up at the same time as the schematic view, if not go to **Hierarchy-Editor** -> **Edit Configuration**). Since you have made changes to cell binding, you should see the icon on the bottom-right corner of the configuration window and the message says update needed as shown in Figure 18. Click on icon at the top menu to update all the changes made in schematic to the configuration, then the dialog as shown in Figure 19 should pop up. Check all cell views and then click OK to update.

Figure 18: Update Changes to Configuration

Figure 19: Update Sync-up

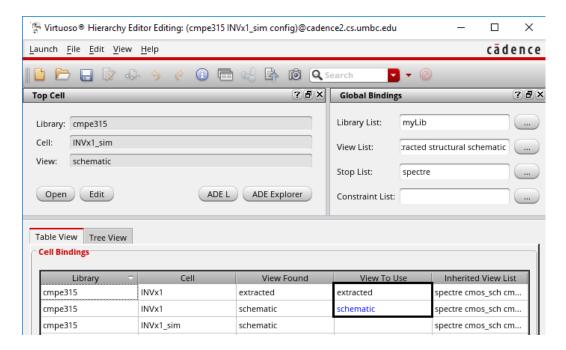

Hierarchy Editor is a very powerful tool. You can bind one or more instances of a master cell to the schematic view and select other instances of the same master to extracted view. For example, if you have multiple instances of INVx1, you can bind one group of instances to schematic view of INVx1 and the other group to extracted view. Figure 20 shows the configuration view after update sync-up between schematic of sim view and configuration has been made. Look carefully at the cell binding table, you could see that in this case some of INVx1 instances were bound to extracted view and others were bound to schematic view. (That is why there are two rows of the same INVx1 cell).

Figure 20: Configuration View after update

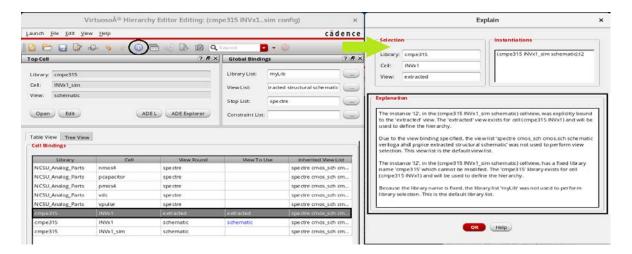

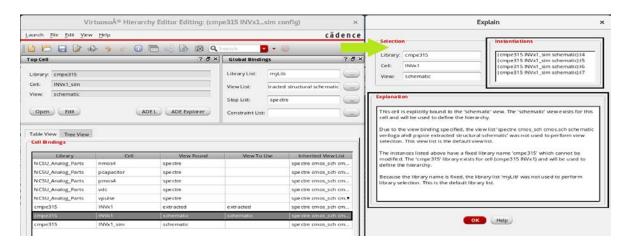

If you have many cell bindings in the configuration and want to make sure that you made the correct binding, you can ask Hierarchy Editor to explain the current binding by select the cell you want to check on the Cell Bindings table, click on 10 icon at the menu bar on the top of the window. Figure 21 and 22 show cell binding

explanations of INVx1 extracted and INVx1 schematic respectively. Do not forget to save configuration view once you are done.

Figure 21: Cell Binding Explain of INVx1 extracted view

Figure 22: Cell Binding Explain of INVx1 schematic view

# **Running Simulation on Extracted Layout**

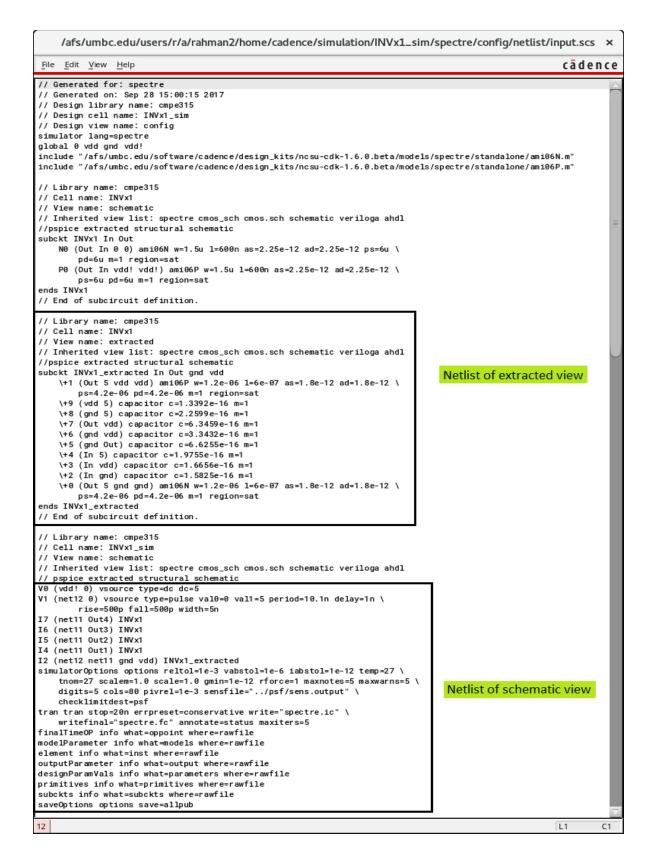

The steps involved in simulation of extracted layout is similar to simulation of schematic, the only requirement is that you need to make the cell binding to the extracted view as explained in the previous section. Please refer to Analog Design Environment Tutorial (available on class website) for more information on how to run simulation. It is a good practice to check the netlist created from simulator in Analog Design Environment to make sure that all the cell bindings you have made are correct before running the simulation. If you use Spectre simulator, go to **Simulation -> Netlist -> Create**. It may take few seconds up to hours for the simulator to generate final netlist depends on the size of the circuit (for the circuits that you design for CMPE315 assignments, they should not take longer than 1 minute).

The final netlist created should show up as shown in Figure 23. In the netlist, there are 5 instances of the inverter, INVx1\_g1, as highlighted in blue in the figure. In the sub-circuit section of the netlist (**subckt** is the keyword for sub-circuit definition) as highlighted in red, the view used for binding to this INVx1\_g1 is the schematic view as shown on the first line of the highlighted region.

```

/afs/umbc.edu/users/r/a/rahman2/home/cadence/simulation/INVx1_sim/spectre/config/netlist/input.scs

cādence

// Generated for: spectre

// Generated on: Sep 28 14:57:22 2017

// Design library name: cmpe315

// Design cell name: INVx1_sim

// Design view name: config

simulator lang=spectre

global 0 vdd!

include "/afs/umbc.edu/software/cadence/design kits/ncsu-cdk-1.6.0.beta/models/spectre/standalone/ami06N.m"

include "/afs/umbc.edu/software/cadence/design_kits/ncsu-cdk-1.6.0.beta/models/spectre/standalone/ami06P.m'

// Library name: cmpe315

// Cell name: INVx1

// View name: schematic

// Inherited view list: spectre cmos_sch cmos.sch schematic veriloga ahdl

//pspice extracted structural schematic

subckt INVx1 In Out

N0 (Out In 0 0) ami06N w=1.5u l=600n as=2.25e-12 ad=2.25e-12 ps=6u \

pd=6u m=1 region=sat

P0 (Out In vdd! vdd!) ami06P w=1.5u l=600n as=2.25e-12 ad=2.25e-12 \

ps=6u pd=6u m=1 region=sat

ends INVx1

// End of subcircuit definition.

// Library name: cmpe315

// Cell name: INVx1 sim

// View name: schematic

// Inherited view list: spectre cmos_sch cmos.sch schematic veriloga ahdl

// pspice extracted structural schematic

Vθ (vdd! θ) vsource type=dc dc=5

V1 (net12 θ) vsource type=pulse val0=0 val1=5 period=10.1n delay=1n \

rise=500p fall=500p width=5n

I7 (net11 Out4) INVx1

I6 (net11 Out3) INVx1

I5 (net11 Out2) INVx1

I4 (net11 Out1) INVx1

I2 (net12 net11) INVx1

simulatorOptions options reltol=1e-3 vabstol=1e-6 iabstol=1e-12 temp=27 \

tnom=27 scalem=1.0 scale=1.0 gmin=1e-12 rforce=1 maxnotes=5 maxwarns=5 \

digits=5 cols=80 pivrel=1e-3 sensfile="../psf/sens.output" \

checklimitdest=psf

tran tran stop=20n errpreset=conservative write="spectre.ic" \

writefinal="spectre.fc" annotate=status maxiters=5

finalTimeOP info what=oppoint where=rawfile

modelParameter info what=models where=rawfile

element info what=inst where=rawfile

outputParameter info what=output where=rawfile

designParamVals info what=parameters where=rawfile

primitives info what=primitives where=rawfile

subckts info what=subckts where=rawfile

saveOptions options save=allpub

L50

C32

```

Figure 23: Netlist of config view using INVx1 schematic

Figure 24 shows the netlist resulted from using multiple views (schematic and extracted) for cell binding. In the figure, there are 4 instances, xi7, xi6, xi5 and xi1, that were bound to schematic view and there is one instance, xi12, that was bound to the extracted view.

## Virtuoso Layout Editor Tutorial

Figure 24: Netlist of config using both extracted and schematic views