Electric Arithmetic, Flip Flops & The DIGISIM Tool

# **Review of Objectives**

After this lecture, you should be able to.....

- Draw a ripple carry adder block diagram

- Use an iterative technique to develop the carry look ahead adder

- Review the different types and function of flip flop used as the basic element of sequential logic and finite state machines

- S-R / D type / T and J-K FF's

- Synchronization: Latch, clocked, edge triggered

# **Full Adder Truth Table**

•  $\mathbf{s}_i = \mathbf{a}_i \oplus \mathbf{b}_i \oplus \mathbf{c}_i$

{ XOR'd inputs }

•  $c_{i+1} = a_i b_i + a_i c_i + b_i c_i$

{after minimization}

| ai | bi | ci | si | ci+1 |

|----|----|----|----|------|

| 0  | 0  | 0  | 0  | 0    |

| 0  | 1  | 0  | 1  | 0    |

| 1  | 0  | 0  | 1  | 0    |

| 1  | 1  | 0  | 0  | 1    |

| 0  | 0  | 1  | 1  | 0    |

| 0  | 1  | 1  | 0  | 1    |

| 1  | 0  | 1  | 0  | 1    |

| 1  | 1  | 1  | 1  | 1    |

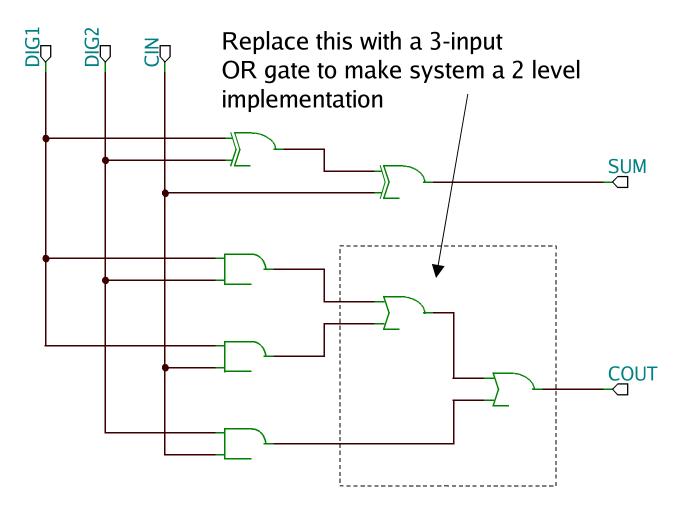

# Full Adder Circuit Using 2-input gates

## **Constructing Larger Adders**

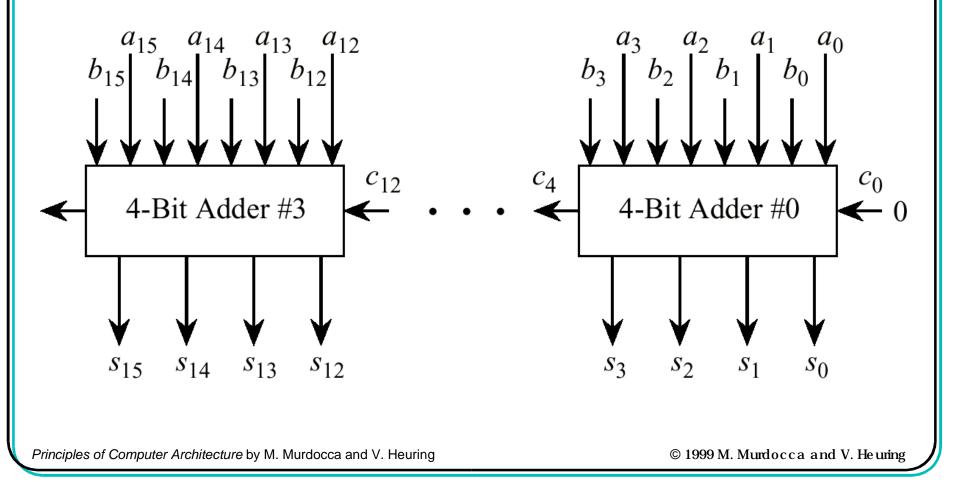

• A 16-bit adder can be made up of a cascade of four 4-bit ripplecarry adders. Circuit gets slower as it gets bigger.....

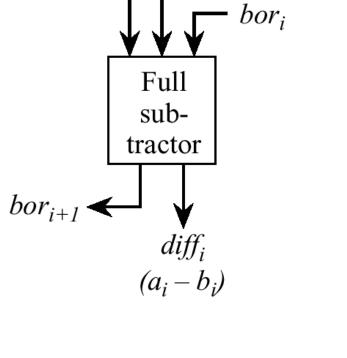

#### **Full Subtractor**

• Truth table and schematic symbol for a ripple-borrow subtractor:

| $a_i$ | $b_i$ | <i>bor</i> <sub>i</sub> | <i>diff<sub>i</sub></i> | $bor_{i+1}$ |

|-------|-------|-------------------------|-------------------------|-------------|

| 0     | 0     | 0                       | 0                       | 0           |

| 0     | 0     | 1                       | 1                       | 1           |

| 0     | 1     | 0                       | 1                       | 1           |

| 0     | 1     | 1                       | 0                       | 1           |

| 1     | 0     | 0                       | 1                       | 0           |

| 1     | 0     | 1                       | 0                       | 0           |

| 1     | 1     | 0                       | 0                       | 0           |

| 1     | 1     | 1                       | 1                       | 1           |

$b_i a_i$

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

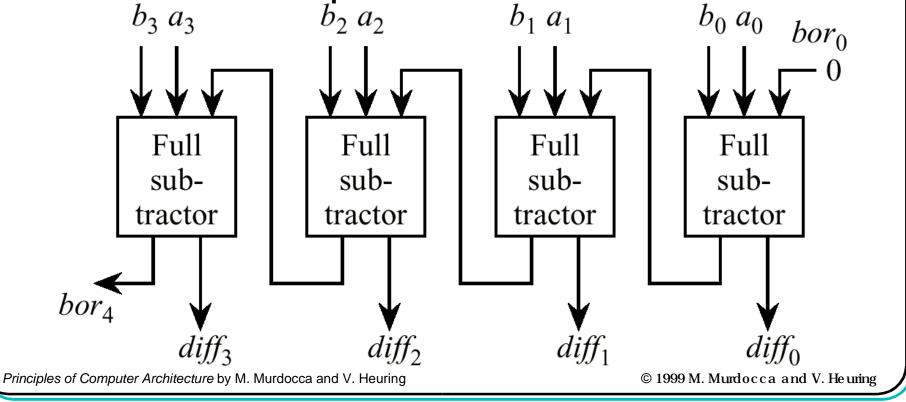

### **Ripple-Borrow Subtractor**

- A ripple-borrow subtractor can be composed of a cascade of full subtractors.

- Two binary numbers A and B are subtracted from right to left, creating a difference and a borrow at the outputs of each full subtractor for each bit position.

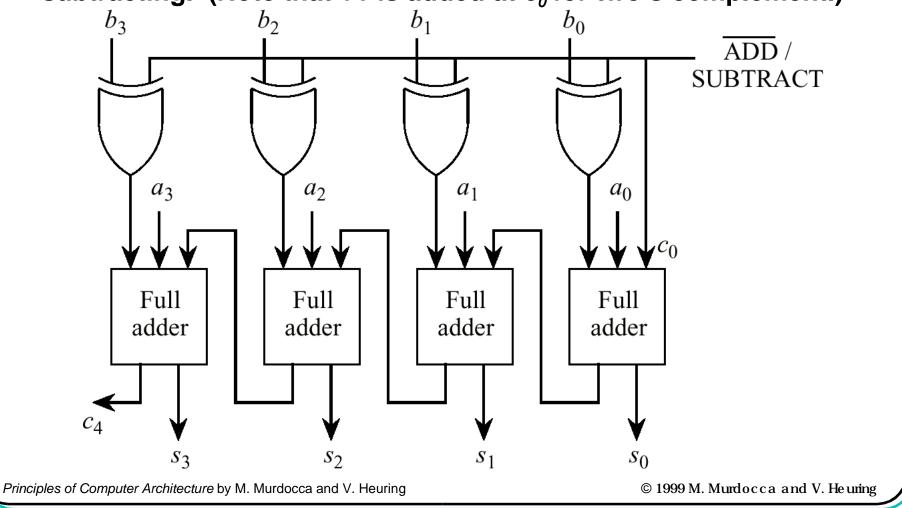

## **Combined Adder/Subtractor**

A single ripple-carry adder can perform both addition and subtraction, by forming the two's complement negative for *B* when subtracting. (Note that +1 is added at c<sub>o</sub> for two's complement.)

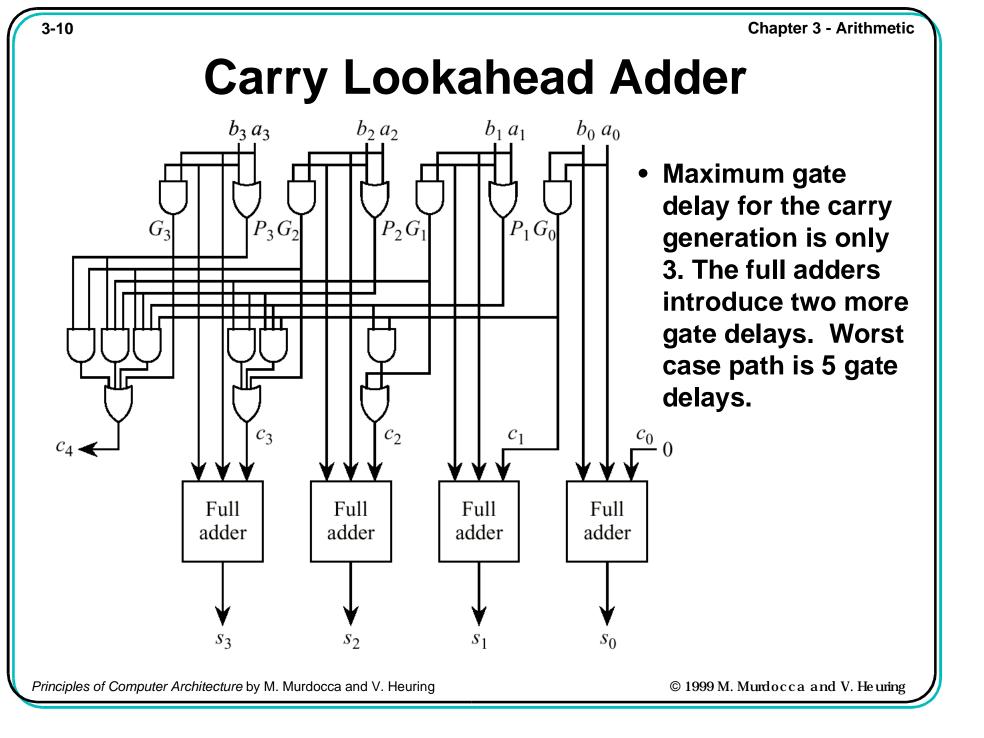

## **Carry-Lookahead Addition**

$$s_{i} = \overline{a_{i}b_{i}c_{i}} + \overline{a_{i}b_{i}c_{i}} + a_{i}\overline{b_{i}c_{i}} + a_{i}b_{i}c_{i}$$

$$c_{i+1} = b_{i}c_{i} + a_{i}c_{i} + a_{i}b_{i}$$

$$c_{i+1} = a_{i}b_{i} + (a_{i} + b_{i})c_{i}$$

$$c_{i+1} = G_{i} + P_{i}c_{i}$$

$$G_{i} = a_{i}b_{i} \text{ and } P_{i} = a_{i} + b_{i}$$

$$c_{0} = 0$$

$$c_{1} = G_{0}$$

$$c_{2} = G_{1} + P_{1}G_{0}$$

$$c_{3} = G_{2} + P_{2}G_{1} + P_{2}P_{1}G_{0}$$

$$c_{4} = G_{3} + P_{3}G_{2} + P_{3}P_{2}G_{1} + P_{3}P_{2}P_{1}G_{0}$$

Principles of Computer Architecture by M. Murdocca and V. Heuring

• Carries are represented in terms of  $G_i$  (generate) and  $P_i$  (propagate) expressions.

Notice that carry terms are generated from inputs and not other carry terms

© 1999 M. Murdocca and V. Heuring

# The Sequential Logic Building Block

# **The Flip Flop**

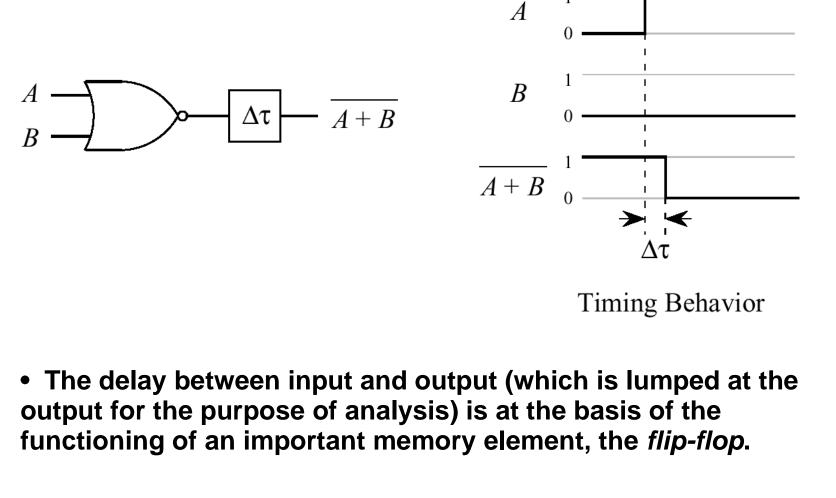

#### **NOR Gate with Lumped Delay**

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

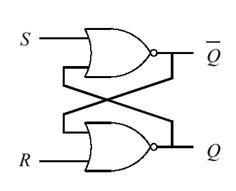

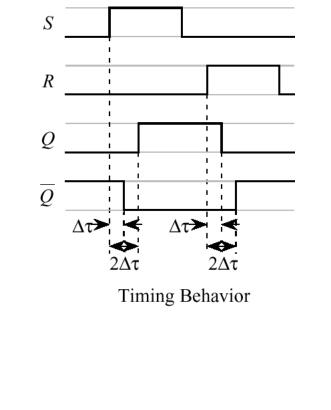

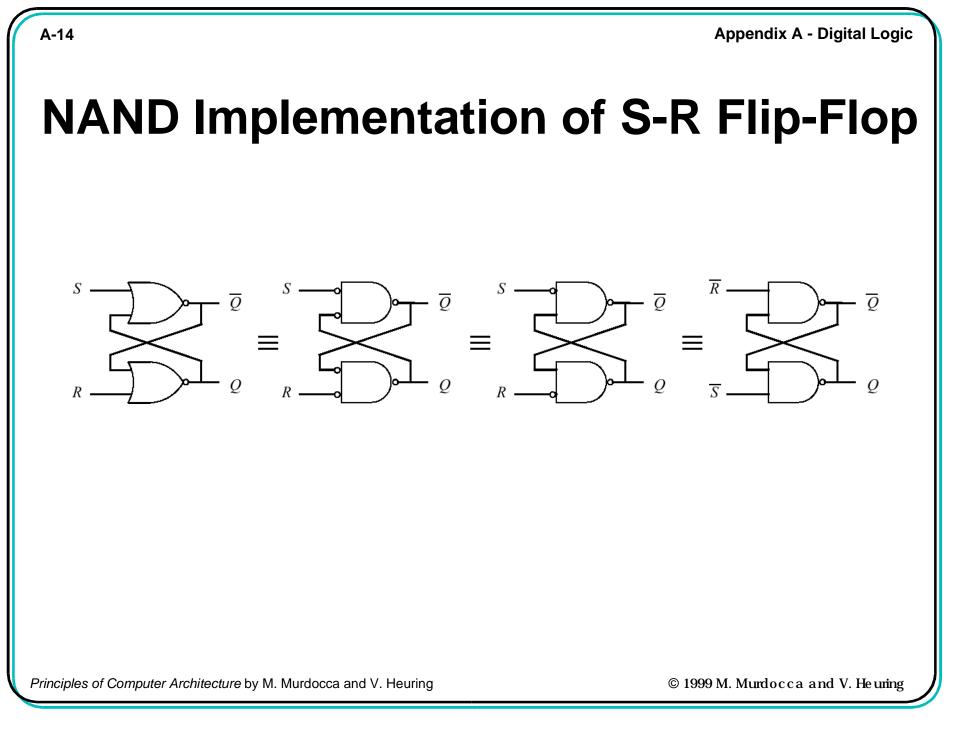

#### **S-R Flip-Flop**

• The S-R flip-flop is an active high (positive logic) device.

| $Q_t$ | $S_t$ | $R_t$ | $Q_{i+1}$    |

|-------|-------|-------|--------------|

| 0     | 0     | 0     | 0            |

| 0     | 0     | 1     | 0            |

| 0     | 1     | 0     | 1            |

| 0     | 1     | 1     | (disallowed) |

| 1     | 0     | 0     | 1            |

| 1     | 0     | 1     | 0            |

| 1     | 1     | 0     | 1            |

| 1     | 1     | 1     | (disallowed) |

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

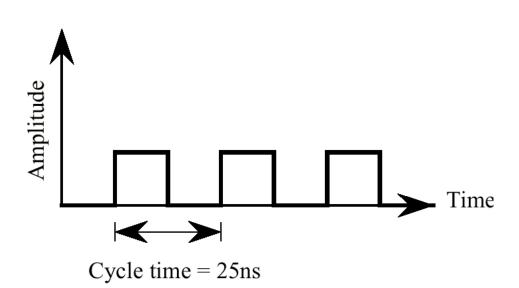

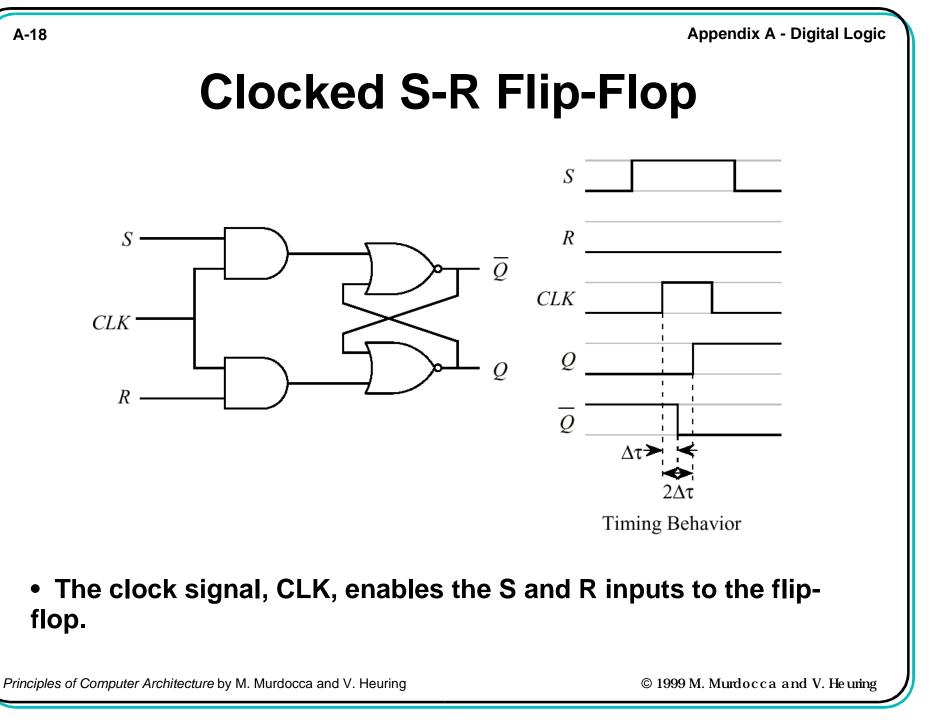

## A Clock Waveform: The Clock Paces the System

• In a positive logic system, the "action" happens when the clock is high, or positive. The low part of the clock cycle allows propagation between subcircuits, so their inputs settle at the correct value when the clock next goes high.

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

#### **Scientific Prefixes**

• For computer memory,  $1K = 2^{10} = 1024$ . For everything else, like clock speeds, 1K = 1000, and likewise for 1M, 1G, *etc.*

| Prefix | Abbrev. | Quantity   | Prefix | Abbrev. | Quantity         |

|--------|---------|------------|--------|---------|------------------|

| milli  | m       | $10^{-3}$  | Kilo   | Κ       | $10^{3}$         |

| micro  | μ       | $10^{-6}$  | Mega   | Μ       | $10^{6}$         |

| nano   | n       | $10^{-9}$  | Giga   | G       | 109              |

| pico   | р       | 10-12      | Tera   | Т       | 1012             |

| femto  | f       | $10^{-15}$ | Peta   | Р       | 10 <sup>15</sup> |

| atto   | а       | $10^{-18}$ | Exa    | E       | $10^{18}$        |

|        |         |            |        |         |                  |

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

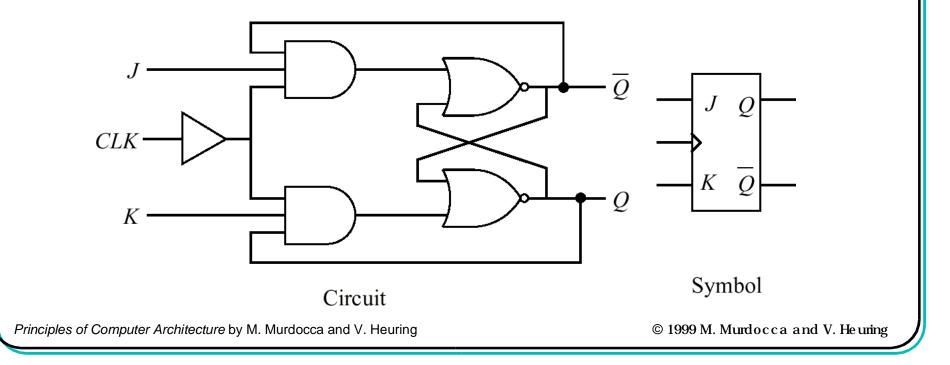

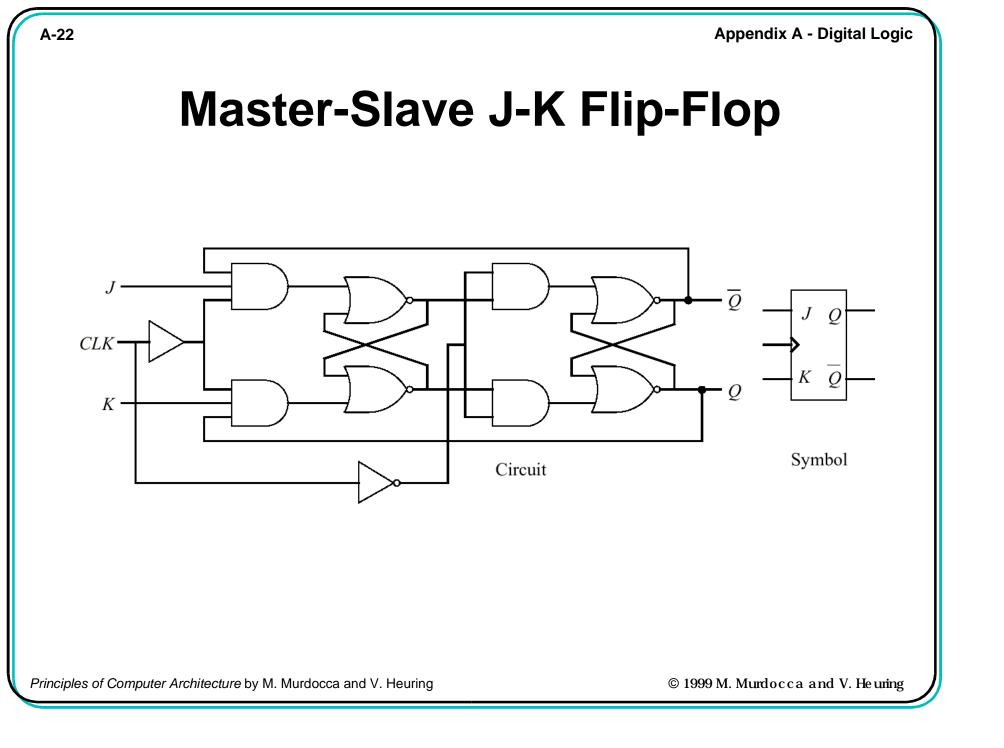

# **Clocked J-K Flip-Flop**

- The J-K flip-flop eliminates the disallowed S=R=1 problem of the S-R flip-flop, because Q enables J while Q' disables K, and vice-versa.

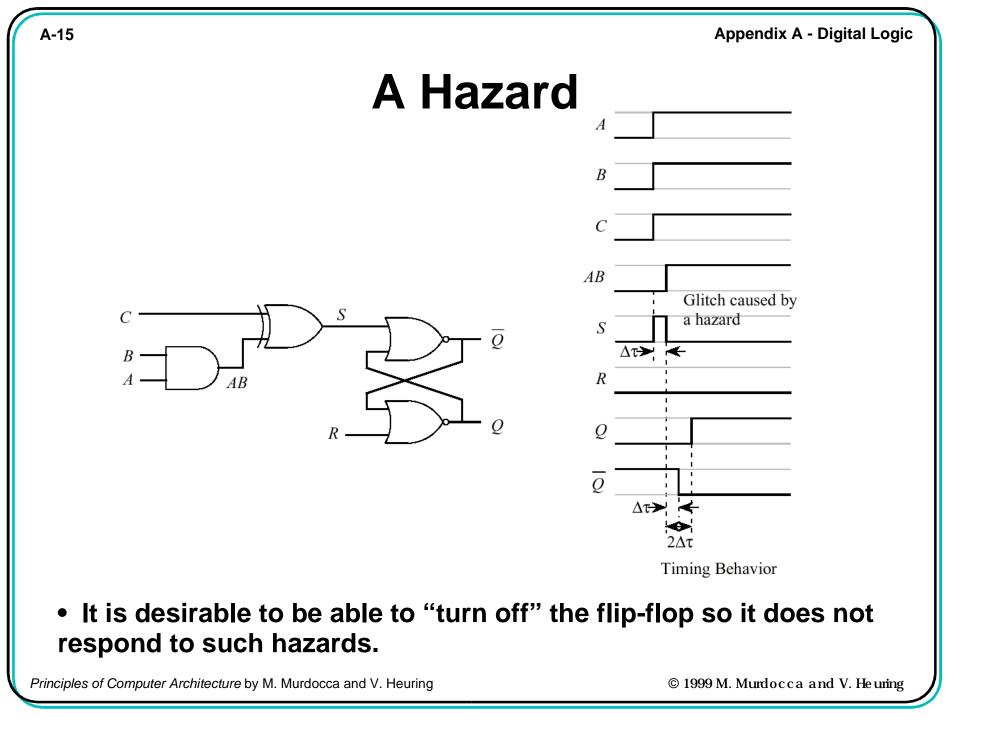

- However, there is still a problem. If J goes momentarily to 1 and then back to 0 while the flip-flop is active and in the reset state, the flip-flop will "catch" the 1. This is referred to as "1's catching."

- The J-K Master-Slave flip-flop (next slide) addresses this problem.

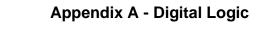

## **Clocked T Flip-Flop**

Circuit

• The presence of a constant 1 at J and K means that the flip-flop will change its state from 0 to 1 or 1 to 0 each time it is clocked by the T (Toggle) input.

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

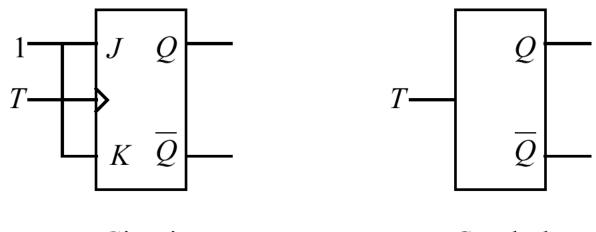

# **Negative Edge-Triggered D Flip-Flop**

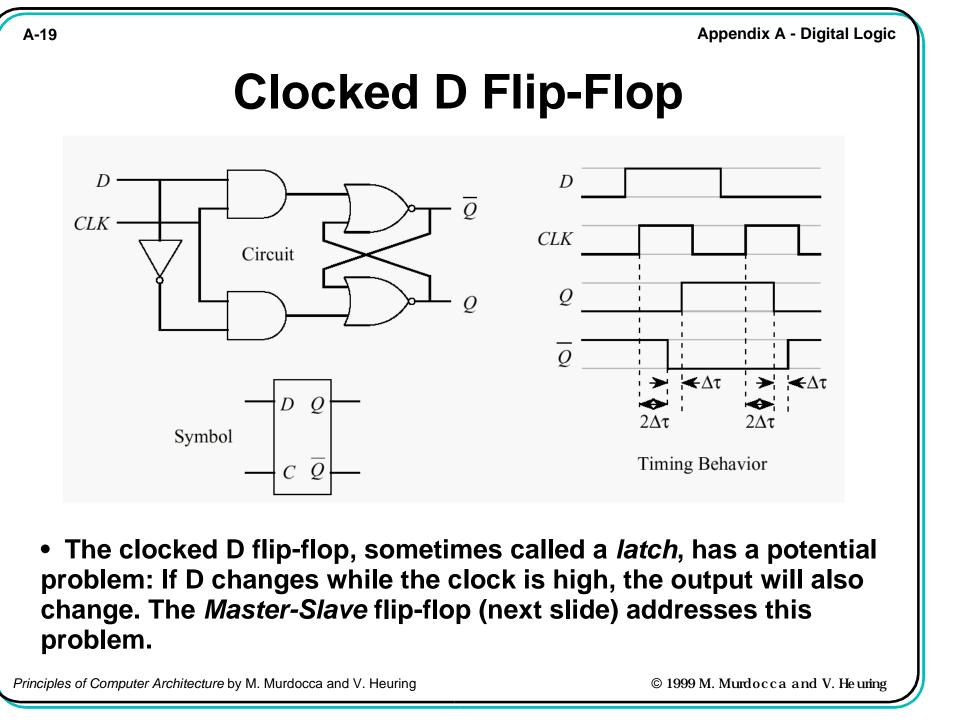

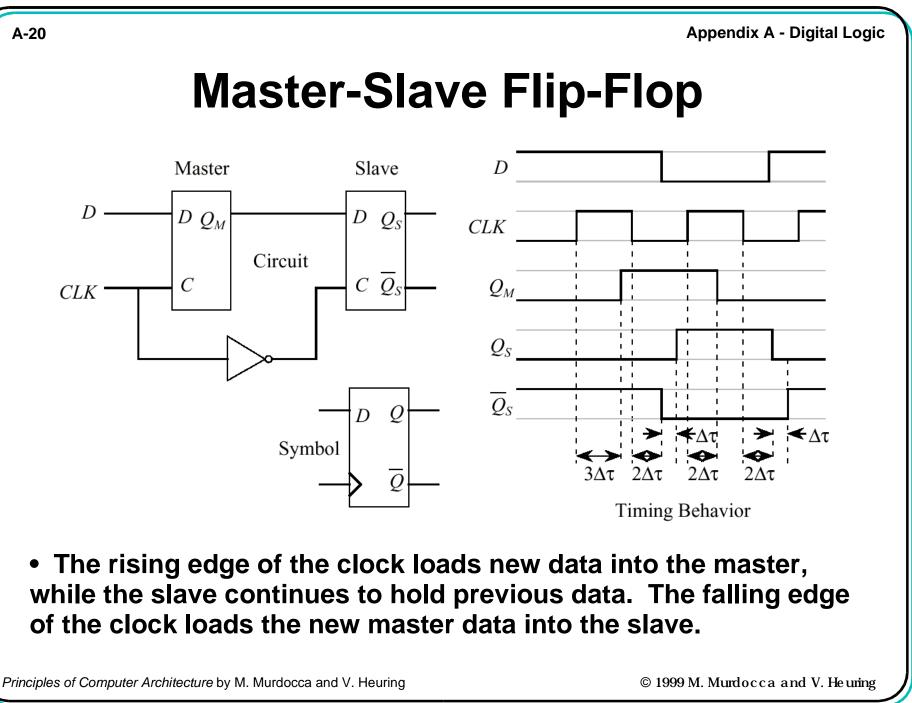

- When the clock is high, the two input latches output 0, so the Main latch remains in its previous state, regardless of changes in D.

- When the clock goes high-to-low, values in the two input latches will affect the state of the Main latch.

- While the clock is low,

D cannot affect the Main latch.

# **Review of Objectives**

We.....

- Constructed a ripple carry adder block diagram

- Developed a faster system called the carry look ahead adder

- Examined the different types and function of flip flop used as the basic element of sequential logic and finite state machines

- S-R / D type / T and J-K FF's

- Synchronization: Latch, clocked, edge triggered

# Digisim

- This can be run on your own PC or through the gl server

- It is a relatively easy tool to use for logic simulation

- Timing diagrams can be generated for sychronous circuit and FSM (finite state machine) validation

- A quick demo follows.....